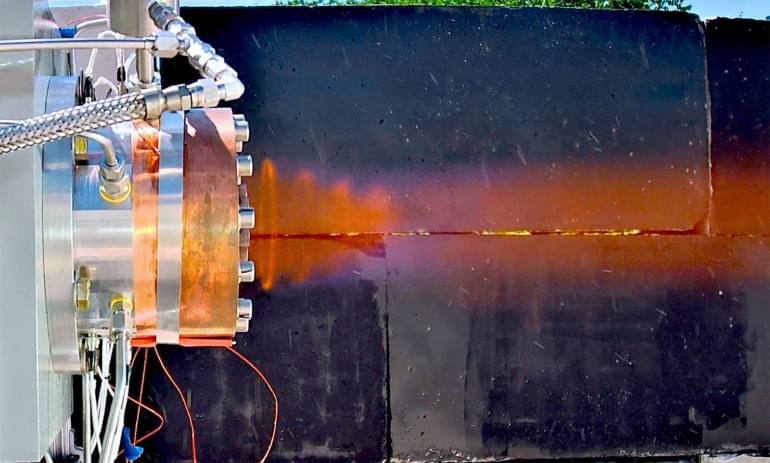

A new fabrication technique for substantially enhancing the prospects of commercializing perovskite solar cells through improved stability, reliability, efficiency and affordability is underway at City University of Hong Kong (CityUHK).

Published in Science, the research is significant because the simple device structure that the CityUHK team has built can facilitate future industrial production and enhance confidence in the commercialization of perovskite solar cells.

“The improvements in stability and the simplification of the production process of perovskite solar cells represent a significant step forward in making solar energy more accessible and affordable,” explained Professor Zhu Zonglong of the Department of Chemistry, explaining that the mineral perovskite is used extensively to convert sunlight into electricity efficiently.