The new method could be the key to getting oxygen to Mars and beyond.

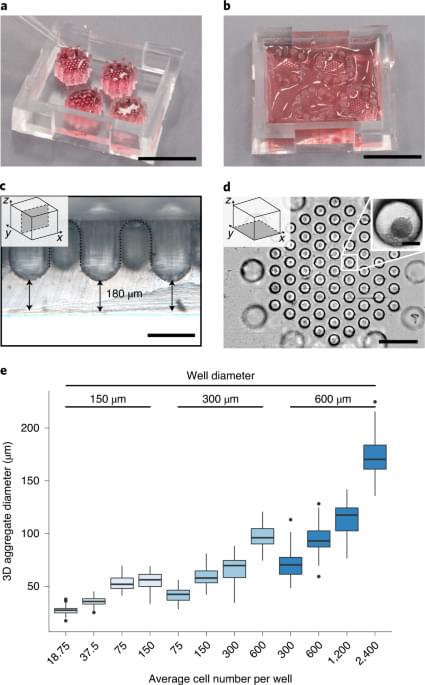

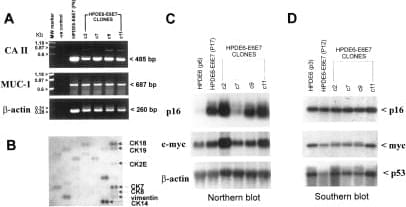

The study was conducted in a special drop tower facility that simulates microgravity conditions. The research proved magnets were effective at producing oxygen. The new method removes gas bubbles from liquids. Producing enough oxygen for astronauts in space is a complicated affair that is only set to become more difficult as we travel to Mars and beyond.

Now, researchers have invented a new way to make oxygen for astronauts using magnets, according to a University of Warwick statement.

Getting oxygen in space using magnets On the International Space Station, oxygen is generated using an electrolytic cell that splits water into hydrogen and oxygen, but then you have to get those gasses out of the system.

A relatively recent analysis from a researcher at NASA Ames concluded that adapting the same architecture on a trip to Mars would have such significant mass and reliability penalties that it wouldn’t make any sense to use, said lead author Álvaro Romero-Calvo, a recent Ph.D. graduate from the University of Colorado Boulder.

NASA currently uses centrifuges to get oxygen in space but those machines are large and require significant mass, power, and maintenance. The new research has conducted practical experiments showcasing magnets could achieve the same results much more practically.

Full Story: