Imec plots a course to 1nm chips, and beyond.

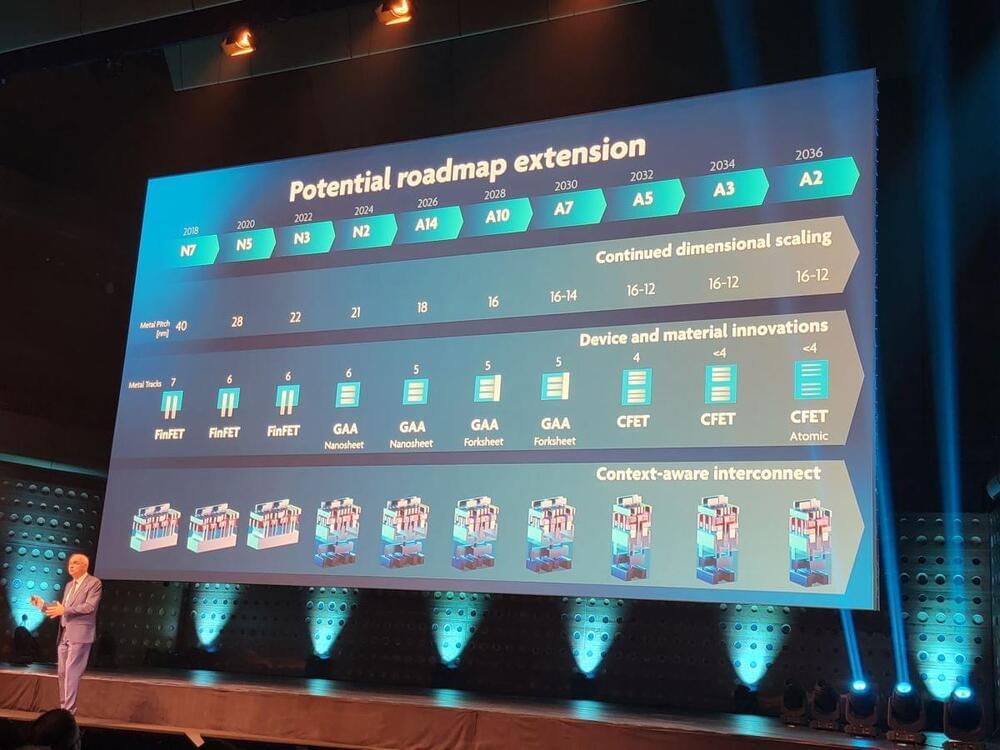

Imec, the most advanced semiconductor research firm in the world, recently shared its sub-‘1nm’ silicon and transistor roadmap at its Future Summit event in Antwerp, Belgium. The roadmap gives us a rough idea of the timelines through 2036 for the next major process nodes and transistor architectures the company will research and develop in its labs in cooperation with industry giants, like TSMC, Intel, Samsung, and ASML, among many others.

The roadmap includes breakthrough transistor designs that evolve from the standard FinFET transistors that will last until 3nm, to new Gate All Around (GAA) nanosheets and forksheet designs at 2nm and A7 (seven angstroms), respectively, followed by breakthrough designs like CFETs and atomic channels at A5 and A2. As a reminder, ten Angstroms are equal to 1nm, so Imec’s roadmap encompasses sub-‘1nm’ process nodes.

You might not have heard of the Interuniversity Microelectronics Centre (imec) before, but it ranks among the most important companies in the world, alongside better-known companies like TSMC and EUV-toolmaker ASML. Think of imec as a silicon Switzerland, of sorts. While the semiconductor research-focused imec doesn’t operate with much fanfare, it serves as the quiet cornerstone of the semiconductor industry, bringing fierce rivals like Intel, TSMC, and Samsung together with chip toolmakers such as ASML and Applied Materials, not to mention the equally-critical semiconductor software design companies (EDA) like Cadence and Synopsys, in a non-competitive environment. This collaboration allows the companies to work together to define the next generation of tools and software they will use to design and manufacture the chips that power the world.