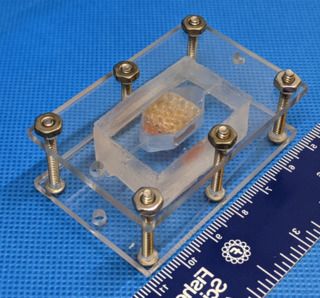

Floorplanning is the process by which an integrated circuit is designed using a top-down view. Rather like the architectural plan of a home, garden, and walkways, each of the major functional blocks is placed in a schematic representation that provides a guide for where everything needs to be. This layout can include transistors, capacitors, resistors, wires and other components, all packed into extremely tiny spaces.

Determining the optimal configuration for processing speed and power efficiency is a detailed and lengthy task, involving many iterations. It can often take weeks or even months for expert human engineers. Attempts to fully automate the process have been unsuccessful.

However, researchers from Google have this week reported a new machine-learning approach to floorplanning. Not only does it reduce the design workload to a matter of hours, it also results in chips with superior designs.